# GALLIUM ARSENIDE AND SILICON FET-TYPE SWITCHES FOR REPETITIVE PULSED POWER APPLICATIONS\*

Xianyue Gu<sup>a</sup>, Charles W. Myles<sup>b</sup>, Andras Kuthi<sup>a</sup>, Qiong Shui<sup>a</sup>, and Martin A. Gundersen<sup>a, ξ</sup>

<sup>a</sup> Department of Electrical Engineering - Electrophysics University of Southern California Los Angeles, CA 90089-0271

<sup>b</sup> Department of Physics, Texas Tech University Lubbock, TX 79409-1051

## Abstract

Repetitive pulsed-power generators with nanosecond rise times and multi-kilovolt outputs commonly employ silicon MOSFET switches. Gallium arsenide FET switches hold the promise of faster operation, higher voltage hold-off, and greater current densities. The realization of this promise requires an understanding of the physical and practical limits of Si- and GaAs-based devices. In this paper, the results of ATLAS simulations on a Si MOSFET and on a GaAs SIT are presented. The results show that GaAs-based devices are superior to those based on Si in terms of switching speeds and power dissipation, but that they have a relatively higher leakage current.

# I. INTRODUCTION

In pulsed generators, the performance of switches can be an important factor that affects the power efficiency, the pulse shape and the repetition rate of pulses. With long life-time and integrating ability, Si Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFET's) are commonly used in multi-kilovolt, hundred amperes pulse systems for fast switching speeds (< 50 ns) [1]. However, Si power MOSFET's have low current rise rates due to the small electron mobility and the narrow energy band gap of Si. In addition, many high-voltage systems require series stacking of switches to reach needed voltages. Because of these effects, it is worthwhile to consider both the limitations of synchronous triggering, and the longterm reliability of the trigger circuit during fast switching transients [2].

Other materials, with wider energy band gaps and larger electron mobilities, such as GaAs, SiC, and diamond have been developed for high-power applications. Among these, GaAs is a good candidate due to its high electron mobility [3] ( $8500 \text{ cm}^2/\text{V}\cdot\text{s}$ ) and relatively mature processing technology. The physical nature of GaAs also promises a higher hold-off voltage capability and a higher operating temperature, in comparison with Si-based switches. Also, since GaAs is a

direct band gap material, the devices based on it have optoelectronic capability, which can result in simple triggering circuits and low-jitter operation. Hadizad *et al.* [1] have found, both theoretically and experimentally, that FET's based on GaAs will dissipate less power than those based on Si. However, GaAs-based FET's have also shown certain fundamental limitations [4].

In this paper, we review some of the practical and physical limitations of Si- and GaAs-based FET switches and present the results of simulations on a Si MOSFET and on a GaAs SIT.

# **II. DEVICE LIMITATIONS**

#### A. Practical Difficulties

It is very difficult to fabricate GaAs-based devices with the purity of typical Si-based devices. The presence of a large concentration of native defects in GaAs, such as EL2 and EL2\*, strongly affects the electrical properties of GaAs-based devices. These defects can be scattering centers and their induced energy levels in the gap can trap electrons. As a result, the observed electron mobility is much less than the theoretical value, about 4000 cm<sup>2</sup>/ V·s for semi-insulating GaAs.

At 300 K, the thermal conductivity for GaAs is about 0.46 watts/cm $\cdot$ C<sup>o</sup>, one third of that for Si [3]. Thermal runaway thus can become a serious issue in designing GaAs power switches for high voltage, high current applications.

#### B. "Lock-on" Effect in GaAs

The "lock-on" effect is a high gain, high field switching mechanism that has been observed in devices fabricated with semi-insulating GaAs and InP [5], but it has not been observed in Si [6]. This effect has been observed with both optical and electronic switch triggering. The lock-on electric field for a given material is independent of the initial bias and of the switch geometry. For GaAs, this field is in the range of  $\sim 3.5 - 9.5$  kV/cm [6]. A detailed discussion of this phenomenon, including experimental data, may be found in reference [7]. This effect causes high forward drop and high power dissipation for bulk

$\xi$  email: mag@usc.edu

<sup>\*</sup> This work was supported by the AFOSR MURI Program and the ARO

switches based on GaAs [6]. Also, it is always accompanied by current filaments [8], which can result in local device and contact damage and thus to a reduced switch lifetime.

A number of models have been proposed to explain the "lock-on" effect, including metastable impact ionization of deep EL2 traps [9]; a combination of double injection, trap filling and avalanche breakdown [10], [11]; and avalanche injection by a transferred electron effect (Gunn effect) [6]. Recently, Hjalmarson *et al.* have developed a collective impact ionization theory to explain the "lock-on" effect in semi-insulating GaAs [12]. The basic idea of this theory is that, at high carrier density ( $n > 10^{17}$ cm<sup>-3</sup>), carrier-carrier scattering leads to a significant increase in the impact ionization probability. This leads to a collective breakdown, which occurs at a much lower field (the lock-on field) than the bulk breakdown field of GaAs.

### **III. DEVICE SIMULATIONS**

In order to compare GaAs- and Si-based switching devices, we have used the ATLAS simulation software to study a vertical Si MOSFET and a recessed gate GaAs Static Induction Transistor (SIT).

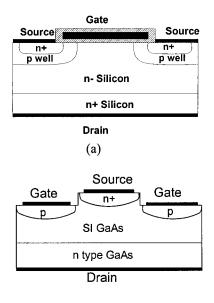

(b)

Figure 1. Cross sectional structure of the switch devices considered here: (a) Si MOSFET and (b) GaAs SIT.

#### A. Device Structure Description

Figure 1 shows a schematic of the cross sectional structures of the Si MOSFET and the GaAs SIT which we have considered. To hold off high voltage, each device has a 30  $\mu$ m epi-layer as the drift region. The n<sup>+</sup> drain regions are doped at n =  $3.5 \times 10^{18}$  cm<sup>-3</sup> to form ohmic contacts. In the GaAs SIT, the p-n junction under the gate is reverse-biased, which introduces a channel potential barrier for electrons under the source. When the gate is

#### **B.** Simulation Results

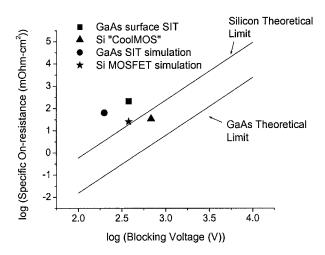

In the ATLAS simulations, we have extracted the specific on-resistance versus blocking voltage for both the Si- and the GaAs-based devices. These are 25.4 m $\Omega$ ·cm<sup>2</sup> and 64.2 m $\Omega$ ·cm<sup>2</sup>, respectively. Figure 2 shows a plot containing our results and the results of others for the specific on-resistance versus blocking voltage in the devices considered here. In that figure, the square and the triangle symbols are experimental results on a GaAs SIT [14] and experimental results on a Si MOSFET [15], while the diamond and the star symbols are the ATLAS simulation results for the GaAs SIT and for the Si MOSFET of Fig. 1. The solid lines in Fig. 2 show the theoretical limits for these Si and GaAs –based devices.

**Figure 2.** Theoretical and experimental specific onresistance, as a function of blocking voltage for GaAs and Si-based switching devices.

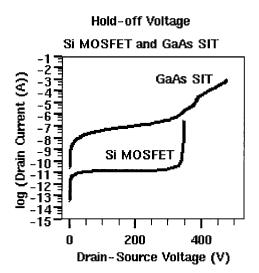

Figure 3 shows our ATLAS simulation results for the drain source current versus drain source voltage of the GaAs SIT and Si MOSFET devices of Fig. 1. From Fig. 3, the hold-off voltage properties of these devices can be obtained. As may be seen in the figure, these voltages are about 370 V for the GaAs SIT and 350 V for the Si MOSFET. For the same drift layer thickness, the GaAs SIT yielded a higher leakage current. This might be an effect of the native defects included in the simulations. In Ref. [14], surface GaAs SIT's with drift layer lengths of 15  $\mu$ m were fabricated and had a drain-source hold-off voltage of ~ 200 V. Since the hold-off voltage is roughly

proportional to the length of the drift region [16], the 370 V obtained in our simulations is about right.

**Figure 3.** Simulation results for drain source current versus drain source voltage for the Si MOSFET and the GaAs SIT considered here. From this figure, the hold-off voltages of the devices can be obtained.

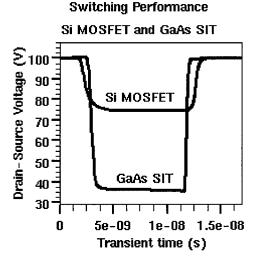

Our ATLAS simulation results for the switching performances of the two devices we have considered are shown in Fig. 4. In that figure, the drain source voltage is plotted as a function of time. In the simulations, the source was connected to ground. The drain resistor was 500 k $\Omega$ , which was connected to a 100 V voltage source. The triggering pulse at the gate had a 2 ns rise time, a 2 ns fall time, and an 8 ns pulse length. As is shown in the plot, the forward voltage drop on the GaAs SIT is much less than that on the Si MOSFET. Also, the SIT gives a fast turn on / turn off capability. These results are consistent with previous theoretical and experimental discussions [1, 4, 17].

**Figure 4.** Switching properties of the Si MOSFET and the GaAs SIT considered here.

#### **IV. SUMMARY**

Using the ATLAS simulation package, we have made a comparison of GaAs SIT and Si MOSFET-type switches for pulsed power applications. Our simulation results show that, due to the higher electron mobility and larger energy band gap of GaAs, the GaAs-based FET has a faster switching speed and greater power efficiency than the Si MOSFET. However, the leakage current of the GaAs-based FET is higher than that of the Si MOSFET.

#### V. REFERENCES

[1] P. Hadizad, M. A. Gundersen, F. Ren, "High-voltage Recessed-gate GaAs Field Effect Transistors", in Proc. of 21<sup>st</sup> International Power Modulator Symposium, 1994, pp. 78-80.

[2] P. Hadizad, J. H. Hur, H. Zhao, K. Kaviani, M. A. Gundersen, and H. R. Fetterman, "A high-voltage optoelectronic GaAs static induction transistor," *IEEE Electron Device Letters*, vol. 14, p. 190, 1993.

[3] S. M. Sze, *Physics of Semiconductor Devices*, Second ed. New York: John Wiley & Sons, 1981.

[4] M. A. Gundersen, "Research issues for new applications of power modulators", in Proc. of 21<sup>st</sup> International Power Modulator Symposium, 1996, pp. 15-17.

[5] G. M. Loubriel, F. J. Zutavern, W. D. Helgeson, D. L. McLaughlin, M. W. O'Malley, and T. Burke, "Physics and Applications of the Lock-on Effect", in Proc. of 8<sup>th</sup> IEEE International Pulsed Power Conference, 1991, pp. 33-36.

[6] M. A. Gundersen, J. H. Hur, H. Zhao, Charles W. Myles, "Lock-on effect in pulsed-power semiconductor switches," *J. Appl. Phys.*, vol. 71, p. 3036, 1992.

[7] S. Kang, "Simulation of High Field Transport in Photoconductive Semiconductor Switches", Ph. D. Dissertation, *Department of Physics*, Texas Tech University, 1998

[8] K. Kambour, S. Kang, C. W. Myles, and H. P. Hjalmarson, "Steady state properties of lock-on current filaments in GaAs", in Proc. of 12<sup>th</sup> Internationa Pulsed Power Conference, 1999, pp. 791 -794.

[9] Larry Partain, Derek Day, Ron Powell, "Metastable Impet Ionization of Traps Model for Lock-on in GaAs Photoconductive switches", *J. Appl. Phys.*, vol. 74, p. 335, 1993.

[10] M. K. Browder and W. C. Nunnally, "Analysis of Nonlinear Photoconductive (NLP) Switching in Bulk GaAs", in Proc. of 8<sup>th</sup> IEEE International Pulsed Power Conference, 1991, pp. 1024 -1027.

[11] R. P. Brinkmann, K. H. Schoenbach, D. C. Stoudt, V. K. Lakdawala, G. A. Gerdin, and M. K. Kennedy, "The

lock-on effect in electron-beam-controlled gallium arsenide switches," *IEEE Transactions on Electron Devices*, vol. 38, p. 701, 1991.

[12] H. P. Hjalmarson, G. M. Loubriel, F. J. Zutavern, D. R. Wake, S. Kang, K. Kambour, and C. W. Myles, "A collective impact ionization theory of lock-on", In Proc. of 12<sup>th</sup> IEEE International Pulsed Power Conference, 1999, pp. 299-302.

[13] M. G. Khazhinsky, "Study of Impurity Modes In Photonic Crystals and Study of Power GaAs MESFETs", Ph. D. Dissertation, *Department of Physics*, Western Michigan University, 1997

[14] P. Hadizad, "A High Voltage GaAs Field-Effect Transistor for Pulsed Switching Applications: The GaAs Static Induction Transistor", Ph.D. Dissertation, Department of Electrical Engineering-Electrophysics, University of Southern California, 1992

[15] G. Deboy, N. Marz, J. -P. Stengl, H. Strack, J. Tihanyi, and H. Weber, "A new generation of high voltage MOSFETs breaks the limit line of silicon", In Proc. of International Electron Devices Meeting,, 1998, pp. 683 -685.

[16] B. J. Baliga, *Modern Power Devices*. New York: John Wiley & Sons, 1987.

[17] P. Hadizad, M. Baik, P. A. Kanjamala, and M. A. Gundersen, "High Power GaAs Static Induction Transistor", In Proc. of 9<sup>th</sup> IEEE International Pulsed Power Conference, 1993, pp. 633-638.